TRACE32를 이용한 Boundary SCAN

Boundary SCAN은 PCB나 IC sub-blocks들의 Interconnects를 테스트 할 수 있는 방법으로 Standard IEEE1149.1에서 정의하고 있습니다. TRACE32에서 지원하는 Boundary SCAN 기능들을 알아보도록 하겠습니다.

목차

1. Overview

TRACE32 Boundary SCAN 기능은 다음과 같은 기능을 지원합니다.

l Flash Programing

l Interactive board connection test

l Automated board connection test

추가적으로 BSDL 파일에서 기술된 모든 Boundary Scan 명령과 Data register들에 대한 Access가 가능합니다.

보통 개발자들은

l Board 조립 후 초기 동작에서 각 칩들간 신호들의 정상적인 연결에 관한 정보

l 각 Port의 상태 측정

l PCB상에서 각 신호들을 Drive하는 작업

l Flash Memory 쓰기/읽기

l IC level에서 build in self tests

l IC 칩에 내장된 Test 기능의 활용

을 사용하고자 합니다.

1.1. 약어

|

BSDL |

Boundary Scan Description Language |

|

DR |

Linux 3.7.0 based Android JellyBean |

|

IR |

Instruction Register |

|

TAP |

Test Access Port |

|

TCK |

JTAG signal, Test ClockInpu |

|

TDI |

JTAG signal, Test Data Input |

|

TDO |

JTAG signal, Test Data Output |

|

TMS |

JTAG signal, Test Mode Select |

|

TRST_N |

JTAG signal, Test ResetInput |

|

PCB |

Printed Circuit Board |

2. Boundary SCAN 구조

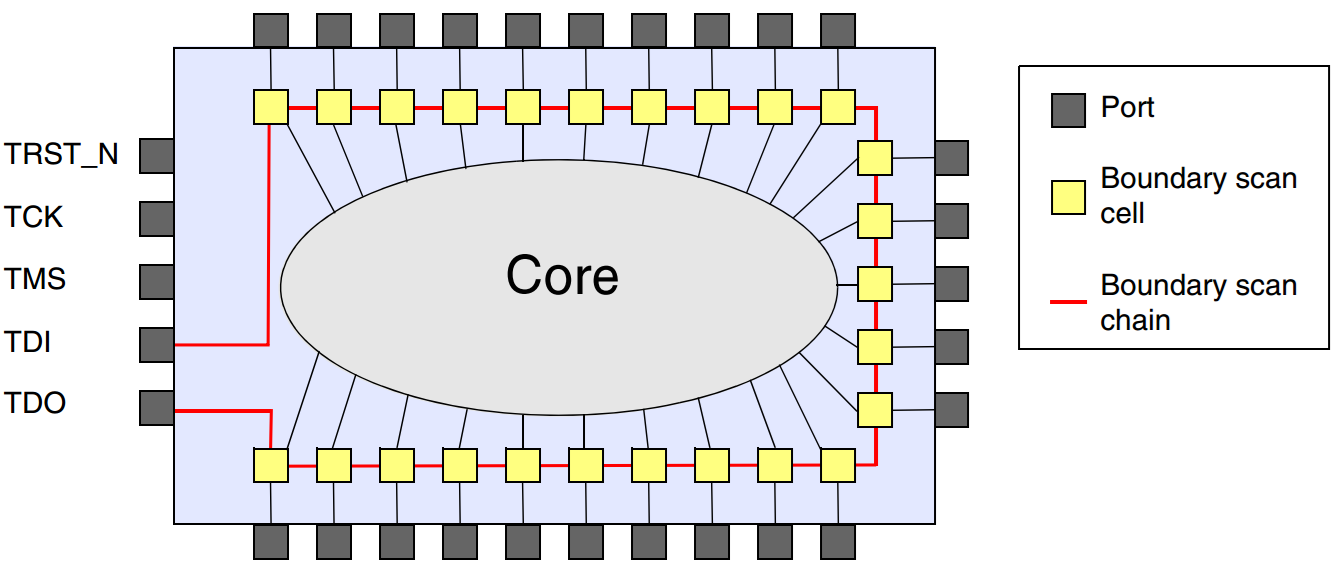

Boundary SCAN 테스트를 위하여 칩을 Design할 때 추가적인 logic들이 칩에 추가되어야 합니다. 즉 아래 그림과 같이 Boundary SCAN Cell이라고 하는 Shift Register로 구성된 Data를 Read/Write할 수 있는 Logic들을 Core와 Port사이에 놓여져야 합니다.

Normal Mode에서는 해당 Cell들은 회로에 영향을 주지 않으며 Core가 각 Port에 바로 연결된 것과 같이 동작하게 됩니다. 만약 Boundary SCAN Mode로 진입하게 되면 Core는 각 Port로부터 Isolation되며 그 때 각 Port의 신호들은 Boundary SCAN을 통해 제어될 수 있게 됩니다. 즉 Boundary SCAN cell들을 통해 각 Port에 값을 쓰거나 읽는 동작이 가능하게 됩니다.

2.1. Boundary SCAN 명령

Boundary SCAN을 위해서는 기본적으로 4가지의 명을을 지원할 수 있도록 JTAG을 Design하여야 하며 추가로 더 많은 명령들을 정의하고 있습니다. 필요에 따라 JTAG Design시 사용자 정의 명령들도 추가할 수 있습니다.

• BYPASS (mandatory): TDI isconnected to TDO via a single shift register.

• SAMPLE (mandatory): Takes a snapshot of the normal operation of the IC.

• PRELOAD (mandatory): Loads data to the boundary scan register.

• EXTEST (mandatory): Apply preloaded data of the boundary scan register to the ports.

• INTEST (optional): Apply preloaded data of the boundary scan register to the core logic.

• RUNBIST (optional): Executes a self-contained self-test of the IC.

• CLAMP (optional): Apply preloaded data of the boundary scan register to the ports and selects the bypass

register as the serial path between TDI and TDO.

• IDCODE (optional): Reads the device identification register.

• USERCODE (optional): Reads and writes a user programmable identification register.

• HIGHZ (optional): Places the IC in an inactive drive state (e.g. all ports are set to high impedance state).

참고로 IC들의 각 Port 정보를 쉽게 얻고 자동화 하여 테스트 할 수 있도록 하기 위하여 각 칩 제조사들은 해당 칩의 JTAG이 지원하는 명령어 List와 각 Port 및 Boundary SCAN cell 들에 대한 정보를 기술하하는 VHDL의 Subset인 BSDL 파일을 제공하고 있습니다. 다음은 BSDL file 예제입니다.

port (

PCIERX7P : inout bit;

PCIERX3P : linkage bit;

:

:

VBUS0 : linkage bit;

USBP0 : inout bit;

SA0_RXP : inout bit;

);

attribute INSTRUCTION_OPCODE of chip: entity is

"EXTEST (0000)," &

"SAMPLE (0001)," &

"TMR (1000)," &

"MBIST (1001)," &

"XMU (1010),"&

"SCAN_DUMP (1011),"&

"DDR_PHY (1100),"&

"TEMP_SEN (1101),"&

"BYPASS (1111)";

attribute REGISTER_ACCESS of chip: entity is

"BYPASS (BYPASS)," &

"BOUNDARY (EXTEST, SAMPLE)," &

"TMR[50] (TMR)," &

"XMU[297] (XMU)," &

"TEMP_SENS[138] (TEMP_SEN), " &

"SCAN_DUMP[732935] (SCAN_DUMP), " & -- E5Q

"DDR3_TDR[196] (DDR_PHY)";

2.2. Boundary SCAN을 위한 JTAG 구조

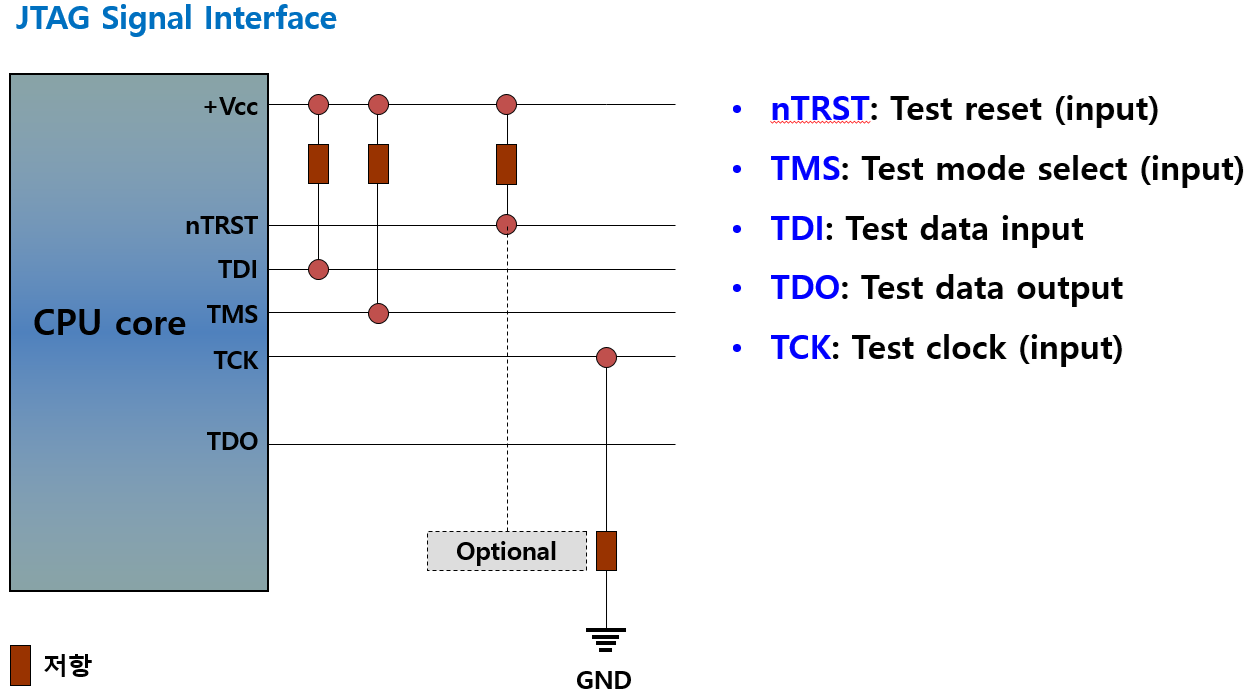

아래 그림은 JTAG Interface에 대한 Schematic입니다.

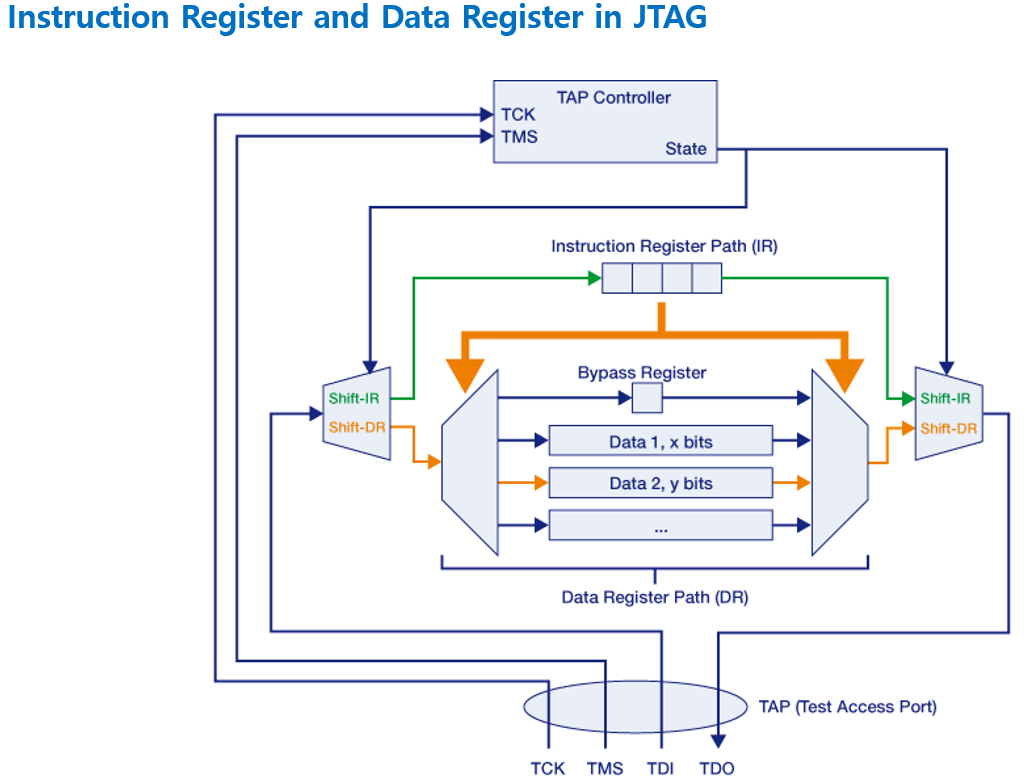

다섯 개의 JTAG신호들을 통하면 아래 그림과 같이 JTAG machine 내에 있는 IR과 DR에 Access가 가능하며 해당 DR에 Boundary SCAN cell 들이 설계 된 경우라면 해당 cell들에 연결된 Port 정보들을 Access 할 수 있게 됩니다. DR은 SoC 설계자가 필요에 따라 추가로 설계 할 수 있습니다.

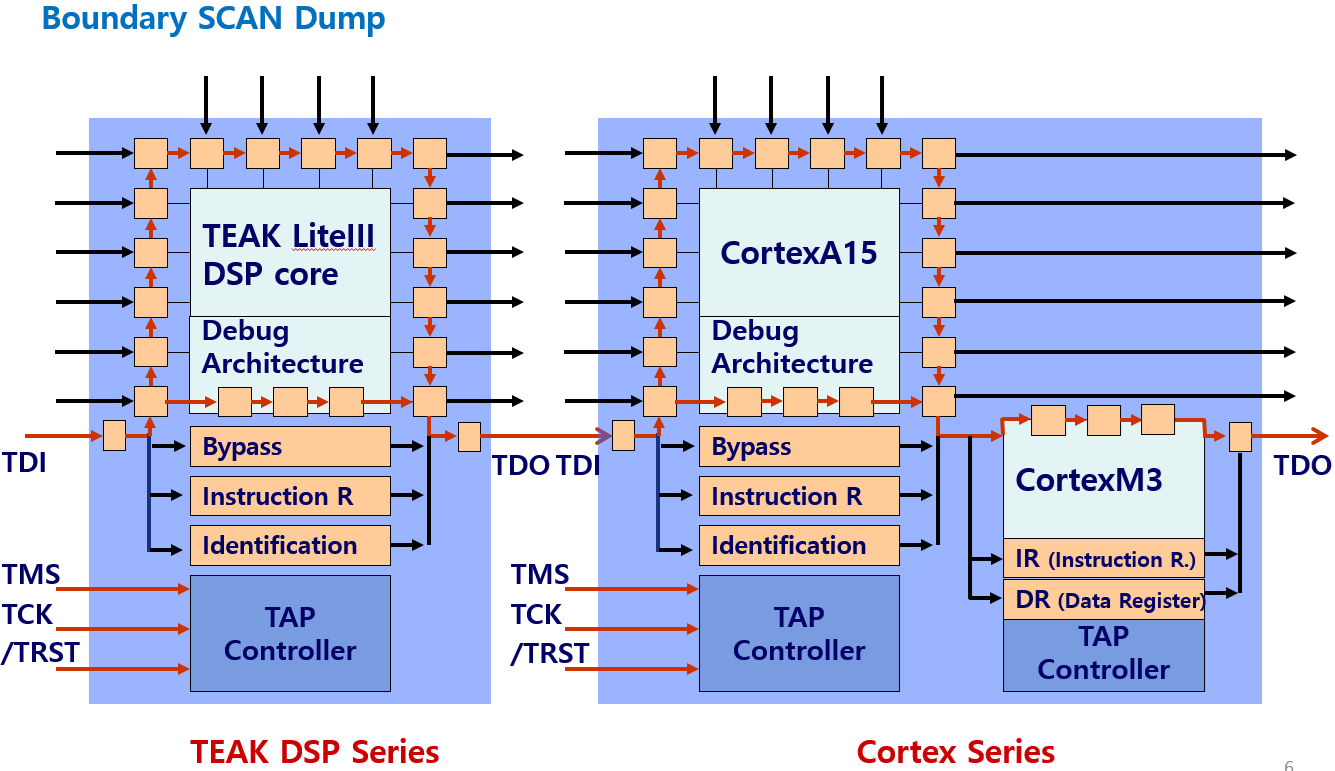

다음 그림은 Board설계 시 JTAG을 Daisy Chain으로 연결하여 설계한 예입니다. JTAG 내 Boundary SCAN을통해 좌측 TEAKLite DSP의 특정 핀에 High를 출력했다면 그 핀에 연결된 우측의 Cortex 칩의 핀에서 그 신호가 읽혀지게 될 것입니다. 만약 출력했던 신호가 우측 칩의 연결된 핀에서 읽혀지지 않는 다면 PCB Board조립에 문제가 있는 것으로 판단할 수 있습니다.

2.3. ARM DAP의 JTAG 명령

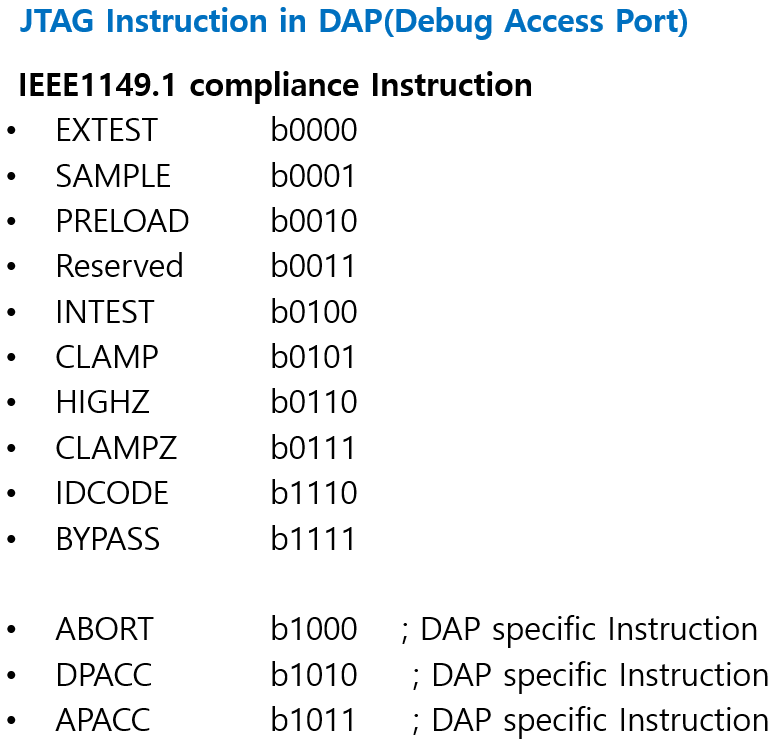

다은 그림은 ARM DAP의 JTAG에서 제공하는 JTAG 명령들을 보여주고 있습니다. Boundary SCAN 명령 뿐 아니라 Debugging을 위한 JTAG 명령들도 있는 것을 확인할 수 있습니다.

3. TRACE32 BSDL 명령

Trace32는 이와 같은 Boundary SCAN을 지원하기 위해 BSDL이라고 하는 명령을 지원하고 있으며 해당 명령을 이용 하면 Boundary SCAN cell로부터 쉽게 데이터를 획득할 수 있습니다.

참고로 BSDL 명령에 의해 지원되는 Boundary SCAN cell 수는 최대 16 Billion cells까지 데이터를 Access할 수 있습니다.

3.1. BSDL 명령

1) BSDL.RES

기존 BSDL 관련 설정 값을 Clear

2) BSDL.UNLOAD [<chip_no.>|ALL]

기존 Boundary SCAN chain으로부터 해당 chip을 삭제

3) BSDL.FILE [<filename>]

BSDL 파일을 로드하고 순서대로 chip_no를 부여함

4) SYStem.JtagClock [frequency]

JTAG으로 사용할 Clock을 정의

5) JTAG.LOCK/JTAG.UNLOCK

Debugger의 JTAG 임의 사용 방지 Lock/Unlock, BSDL 윈도우는 현재 상태를 보여줌

6) BSDL.HARDRESET

nTRST핀을 이용하여 TAP 컨트롤러를 Reset하고 Select-DR-SCAN state로 변경

7) BSDL.SOFTRESET

TMS=1 후 TCK clock을 5번 입력하여 TAP controller를 Reset State로 변경 후 Select-DR-SCAN

state로 변경

8) BSDL.CHECK.BYPASS()

Boundary SCAN BYPASS 테스트 후 성공하면 TRUE를 return함

9) BSDL.CHECK.IDCODE()

Boundary SCAN IDCODE 테스트 후 성공하면 TRUE를 return 함

10) BSDL.BYPASSall

JTAG chain의 모든 IR에 BYPASS 후 무작위 패턴 입력 후 출력에 체크되는 지 확인, 만약 실패하면

입력 패턴과 출력 패턴 경고 메시지로 출력

11) BSDL.IDCODEall

JTAG chain의 모든 IR에 IDCODE 명령 후 IDCODE 확인, 만약 IDCODE 명령이 없는 경우 BYPASS

명령 입력

12) BSDL.SAMPLEall

JTAG Chain의 모든 IR에 SAMPLE 명령 입력 후 Boundary SCAN chain의 값들을 Sample하여 읽

오는 테스트 명령

13) BSDL.RUN IR

BSDL.SET에 의해 선택된 IR 명령을 IR에 밀어 넣는 명령

14) BSDL.RUN DR

BSDL.RUN IR에 의해 선택된 DR Access명령으로 BSDL.SET 명령에 의해 설정된 Write Buffer 데이

터를 DR에 씀과 동시에 DR로부터 Read Buffer로 읽어 들임

15) BSDL.RUN

BSDL.RUN IR 명령 실행 후 BSDL.RUN DR명령도 실행

16) BSDL.SET [<chip no.>] IR [IR 명령]

BSDL.RUN IR 명령 실행 시 밀어 넣을 IR명령 선택 명령, Ex) BSDL.SET 1. BYPASS

17) BSDL.SET [<chip no.>] DR [DR cell] [0|1|H|L|Z|X]

BSDL.RUN DR 실행 시 설정할 값을 Write Buffer에 세팅하는 명령

EX) BSDL.SET 1. DR USBTXD 0

BSDL.SET 3. DR * SAMPLE

18) BSDL.SET 1. Option BSRHISTORY ON

Boundary SCAN Register에 한해 읽어 낸 기존 값들 history 보여주는 옵션

19) BSDL.SELect [<chip no.>]

SCAN chain에 연결된 여러 칩들 중 설정/읽기를 원하는 칩 선택명령

20) BSDL.SToreDR [<chip no.>] [Data Register name] [filename to store] /BINary

BSDL.RUN DR 명령에 의해 읽혀진 Read Buffer의 값을 파일로 저장

21) BSDL.LoadDR [<chip no.>] [Data Register name] [filename to load] /BINary

BSDL.SToreDR명령에 의해 저장된 데이터를 다시 로드 하는 명령

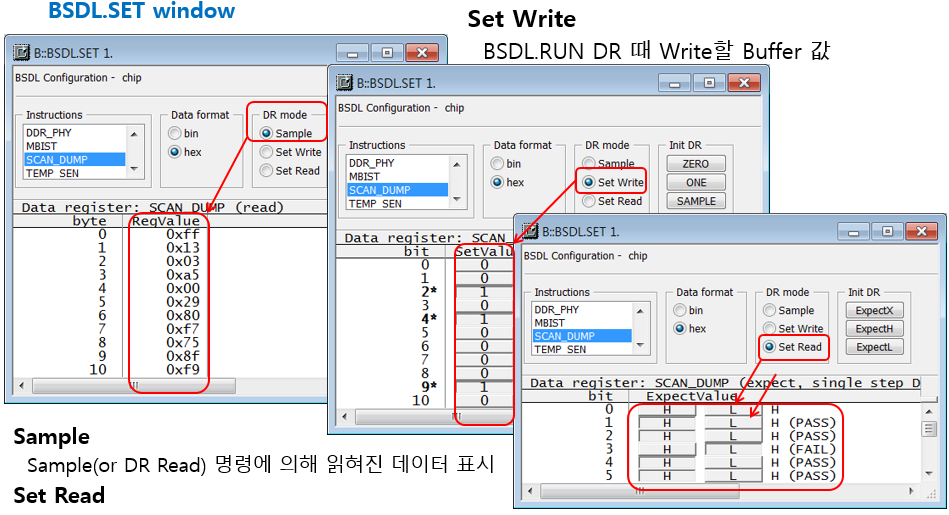

다음은 BSDL명령을 통해 Boundary SCAN Cell들에 데이터를 Access하는 예를 보여주고 있습니다. 이와 같이TRACE32는 JTAG을 이용한 SW Debugging 뿐아니라 Boundary SCAN을 이용한 Board 테스트까지 자유롭게 개발할 수 있는 환경을 제공합니다.